嵌入式硬件系统基础

嵌入式硬件系统基本组成

- 嵌入式微处理器为核心的SoC(系统级芯片/片上系统)

- 总线

- 存储器

- 输入/输出接口和设备

微处理器

冯·诺伊曼结构指令和数据都放在同一个存储空间中,统一编制,通过同一个总线访问。

哈佛结构中程序和数据存储在不同的存储空间中,单独编制,通过两条总线访问,吞吐率提高了一倍。

精简指令集RISC和复杂指令集CISC对比:

| CISC | RISC | |

|---|---|---|

| 价格 | 硬件实现软件功能,硬件复杂,成本高 | 软件实现硬件功能,软件复杂,成本低 |

| 性能 | 代码尺寸小,执行周期数多 | 流水线结构,代码尺寸大,执行周期数少 |

| 指令集 | 混杂型指令,简单,复杂混杂 | 简单的指令 |

| 高级语言支持 | 硬件实现 | 软件实现 |

| 寻址模式 | 复杂的寻址模式,支持内存到内存寻址 | 简单寻址模式,仅允许LOAD和STORE指令寻址 |

| 控制单元 | 位码 | 直接执行 |

| 寄存器数量 | 寄存器较少 | 寄存器较多 |

主流的嵌入式微处理器体系结构:ARM、MIPS、PowerPC、SH、X86等。

总线

总线是CPU与存储器和设备通信的机制,是计算机各部件之间传送数据、地址和控制信息的公共通道。

嵌入式系统总线分类:

- 按照相对于CPU的位置划分

- 片内总线

- AMBA

- AVALON

- OCP

- WISHBONE

- 片外总线

- 片外并行总线

- PCI

- ISA

- 片外串行总线:串行总线是指按位传送数据的通路,其连接线少、接口简单、成本低、传送距离远,被广泛用于嵌入式系统与外设的连接和计算机网络。

- UART

- SPI

- I2C

- USB

- 片外并行总线

- 片内总线

- 按功能和信号类型分类

- 数据总线 Dbus

- 地址总线 Abus

- 控制总线 Cbus

由CPU Core选择片内总线的类型,由应用程序选择片外总线选型。

总线参数:

- 总线宽度(位宽)

- 总线频率(MHz)

- 总线带宽(数据传送率,每秒最大传输的数据量)(总线带宽=(总线宽度/8)*总线频率)

****

****

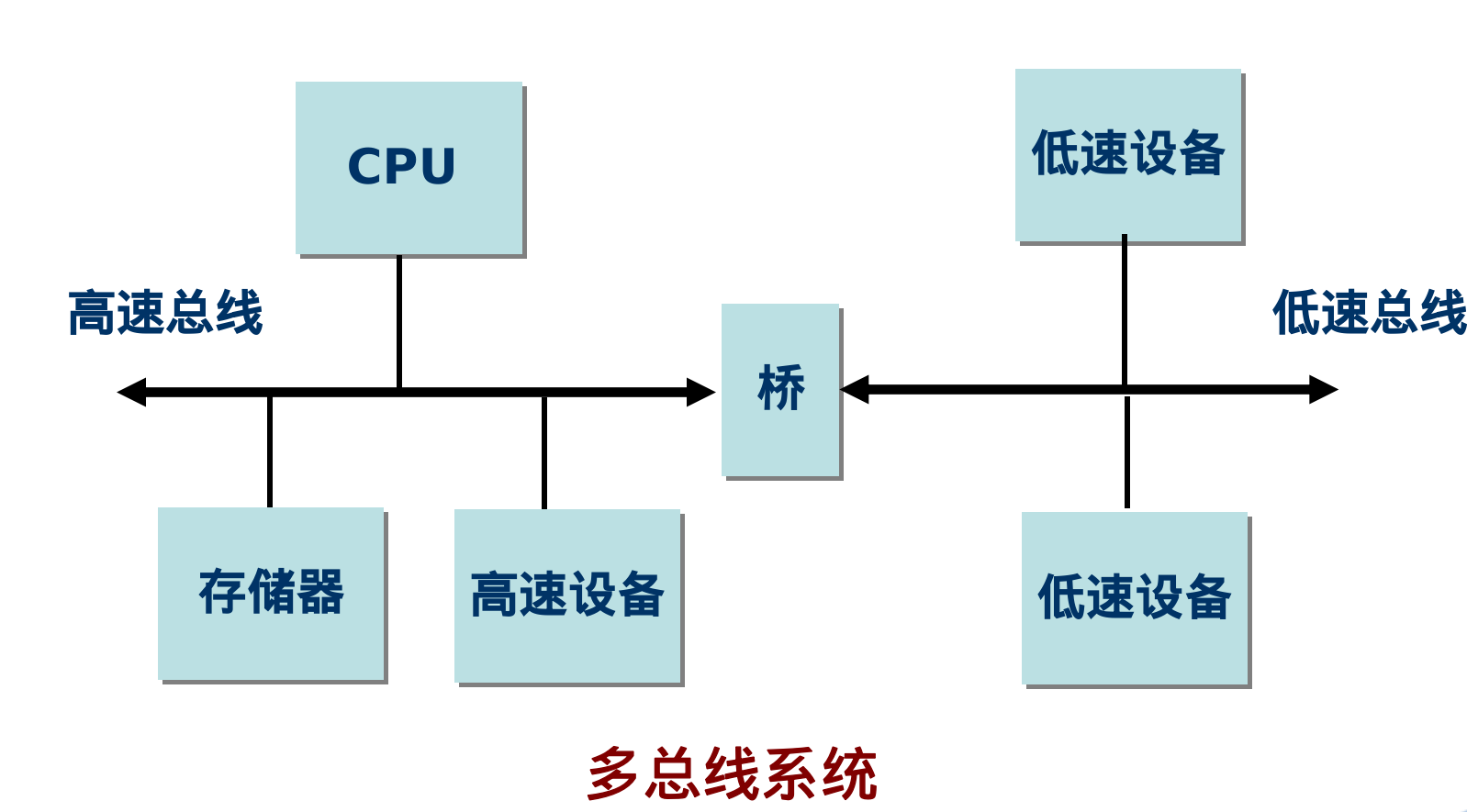

嵌入式系统可能含有多条总线。

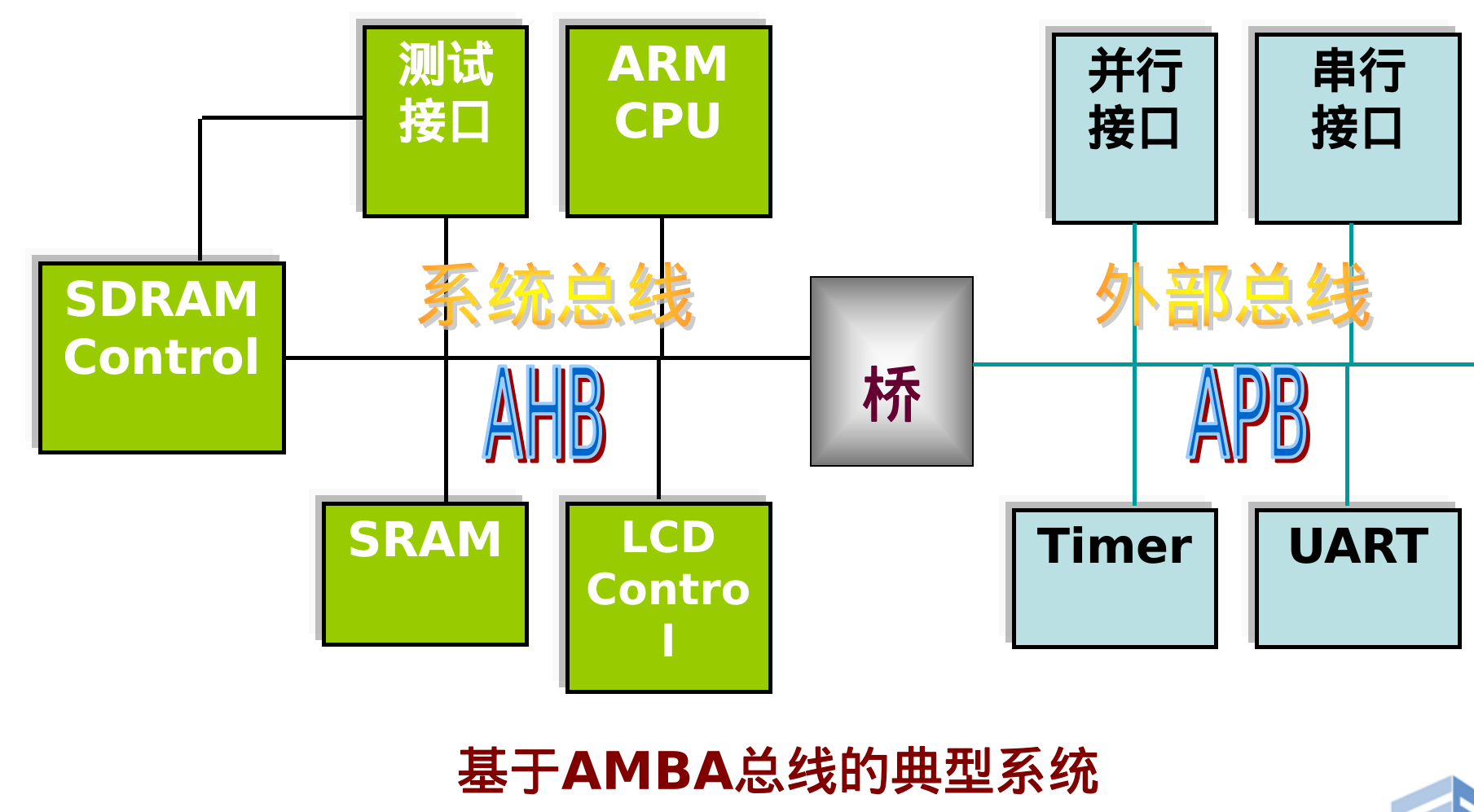

AMBA总线

AMBA(Advanced Microcontroller Bus Architecture)是ARM 公司研发的一种总线规范。

AMBA总线规范中的三种总线:

- 高级高性能总线 AHB(Advanced High-performance Bus)用于高性能系统模块的连接,支持突发模式数据传输和事务分割;可以有效地连接处理器、片上和片外存储器,支持流水线操作。

- 高级系统总线 ASB(Advanced System Bus)也用于高性能系统模块的连接,为AHB总线替代

- 高级外设总线 APB(Advanced Peripheral Bus)用于较低性能外设的简单连接,一般是接在AHB或ASB系统总线上的第二级总线。

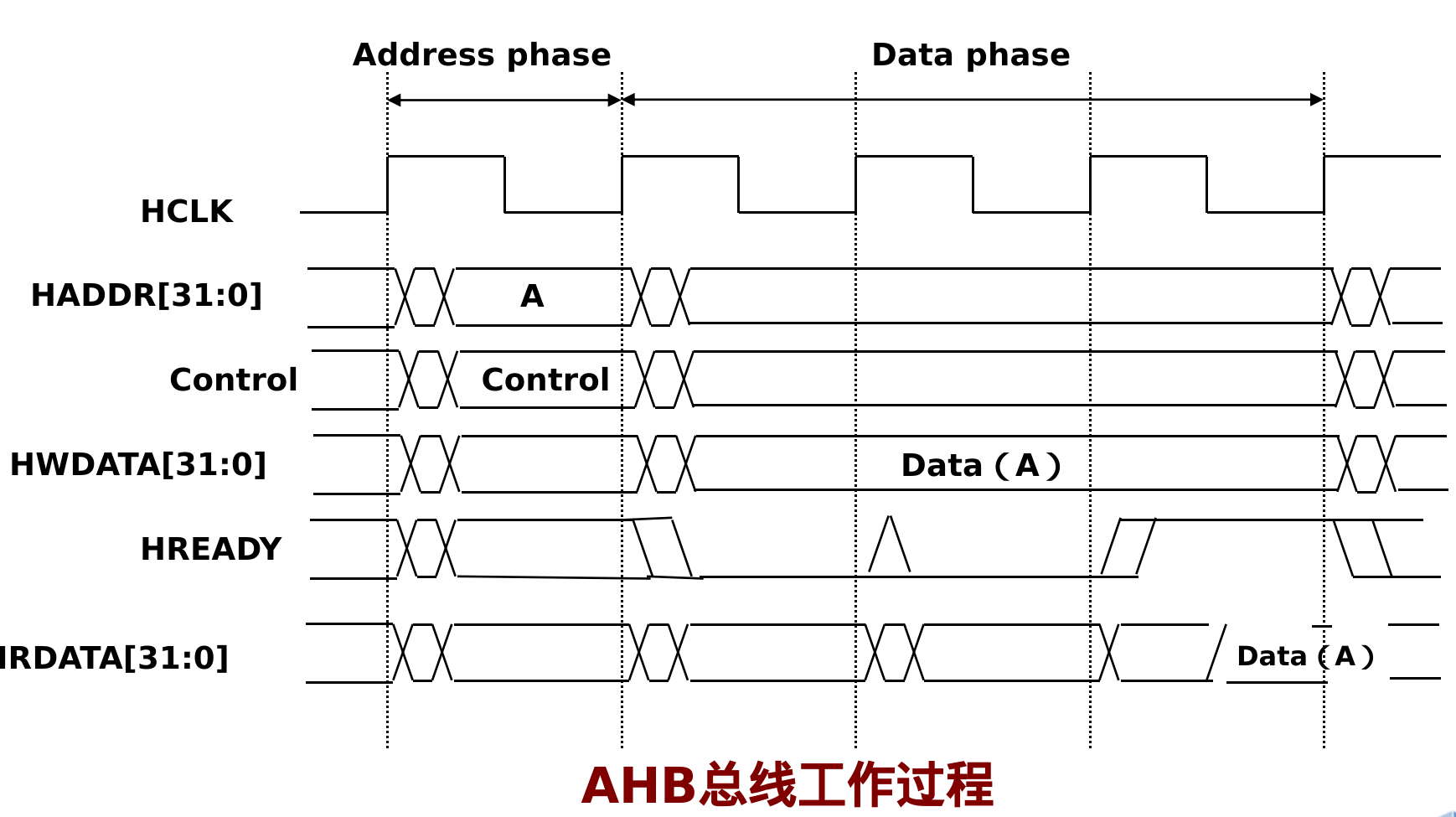

AHB总线

构成:

- 主单元:只有主单元可在任何时刻使用总线。AHB可以有一个或多个主单元。主单元可以是RISC处理器、协处理器以及DMA控制器,以启动和控制总线操作。

- 从单元:可以响应(并非启动)读或写总线操作;总线的从单元可以在给定的地址范围内对读写操作进行相应的反应。从单元向主单元发出成功、失败信号或等待各种反馈信号。从单元通常是其复杂程度不足以成为主单元的固定功能块,例如外存接口、总线桥接口以及任何内存都可以是从单元,系统的其他外设也包含在AHB的从单元中。

- 仲裁器:用来确定控制总线是哪个主单元,以保证在任何时候只有一个主单元可以启动数据传输。一般来说仲裁协议都是固定好的,例如最高优先级方法或平等方法,可根据实际的情况选择适当的仲裁协议。

- 译码器:总线译码器用于传输译码工作,提供传输过程中从单元的片选信号。

工作阶段:

- 地址传送阶段(address phase):它将只持续一个时钟周期。在HCLK的上升沿数据有效。所有的从单元都在这个上升沿来采样地址信息。

- 数据传送阶段(data phase):它需要一个或几个时钟周期。可以通过HREADY信号来延长数据传输时间,当HREADY信号为低电平时,就在数据传输中加入等待周期,直到HREADY信号为高电平才表示这次传输阶段结束。

APB总线

构成:

- APB桥:APB桥是APB中唯一的主单元,是AHB/ASB的从单元。APB桥将系统总线AHB/ASB和APB连接起来,并执行下列功能:

- 锁存地址并保持其有效,直到数据传送完成。

- 译码地址并产生一个外部片选信号,在每次传送时只有一个片选信号(PSELx)有效。

- 写传送(write transfer)时驱动数据到APB。

- 读传送(read transfer)时驱动数据到系统总线AHB/ASB。

- APB从单元(Slave):APB从单元具有简单灵活的接口,接口的具体实现是依赖于特定设计的,有许多不同的可能。当写传送时数据锁定在下列点:

- 当PSELx为高电平时,在每个PCLK的上升沿,在PENABLE的上升沿。

- 片选信号PSELx和地址信号PADDR可合并起来决定需要操作的寄存器。

PCI总线

1991年Intel公司联合IBM、Compaq、AST、HP、DEC等100多家公司成立了PCISIG(Peripheral Component Interconnect Special Interest Group)协会,它致力于促进PCI(Peripheral Component Interconnect)总线工业标准的发展。PCI总线的特点:

- PCI总线是地址、数据多路复用的高性能32位和64位总线。

- 32位PCI 有120引脚,64 位有184引脚。

- 从数据宽度上看,PCI 总线有32bit 、64bit 之分

- 从总线速度上分,有33MHz、66MHz、133MHz

- 总线带宽为133MB/s到超过1GB/s

PCI 总线的地址总线与数据总线是分时复用(分时复用的好处是一方面可以节省接插件的管脚数,另一方面便于实现突发数据传输)的,支持即插即用(Plug and Play) 、中断共享等功能。

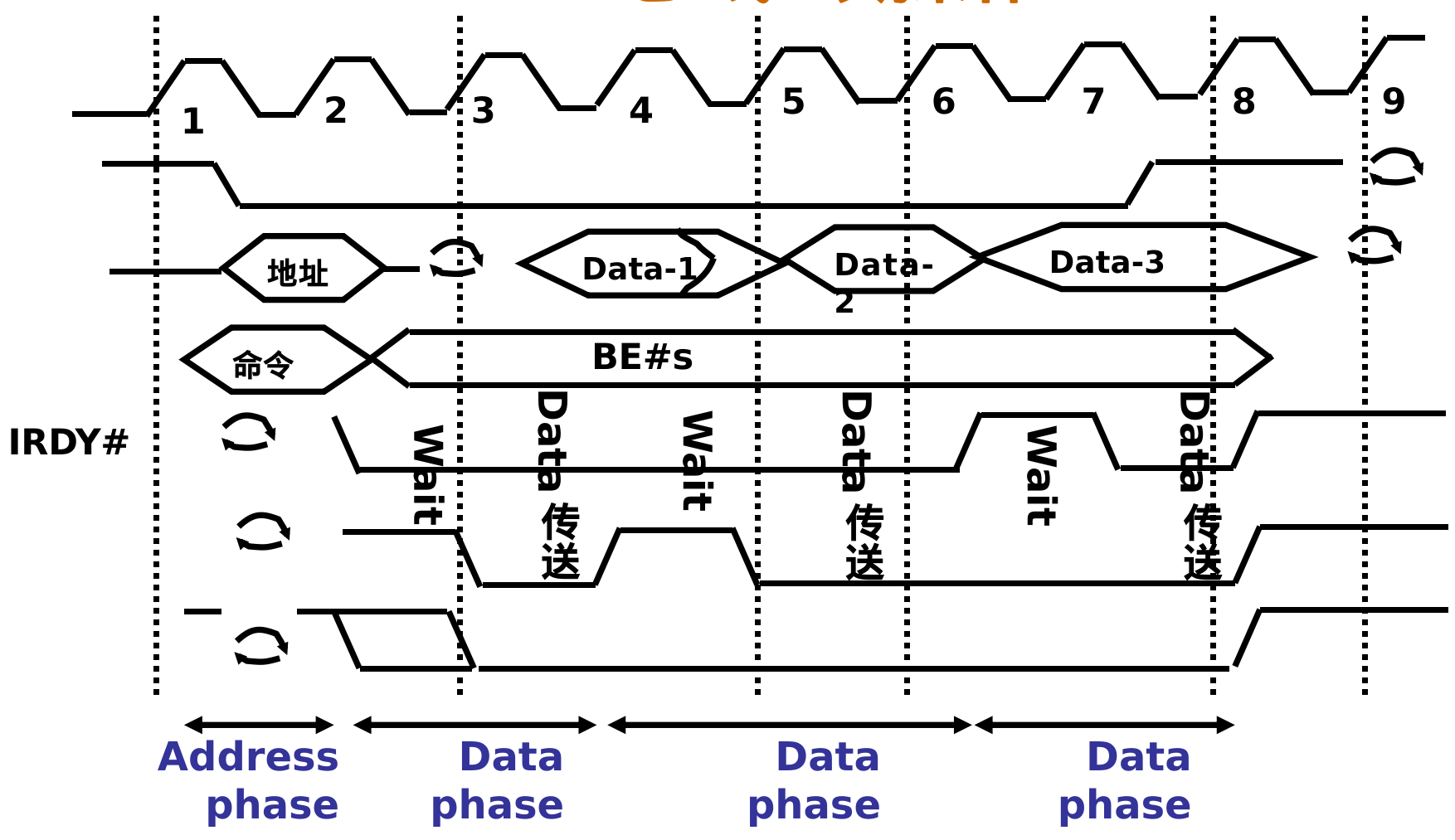

数据传输时,由一个PCI 设备做发起者(主控、Initiator或Master),而另一个PCI 设备做目标(从设备、Target 或Slave)。总线上所有时序的产生与控制都由Master来发起。PCI 总线在同一时刻只能供一对设备完成传输,这就要求有一个仲裁机构,来决定谁有权拿到总线的主控权。

PCI总线信号定义:

- 系统控制类:

- CLK:PCI 时钟,上升沿有效

- RST:Reset信号

- 传输控制:

FRAME #:标志传输开始与结束

IRDY#:Master 可以传输数据的标志

DEVSEL #:当Slave 发现自己被寻址时设置低电平应答

TRDY#:Slave 可以传输数据的标志

STOP #:Slave主动结束传输数据

IDSEL:在即插即用系统启动时用于选中板卡的信号

地址与数据总线

- AD[ 31 : :0 ]:地址/数据分时复用总线

- C/ BE # [3 : :0 ]:命令/字节使能信号

- PAR:奇偶校验信号

仲裁信号

- REQ #:Master 用来请求总线使用权

- GNT #:仲裁机构允许Master得到总线使用权

错误报告

- PERR #:数据奇偶校验错

- SERR #:系统奇偶校验错

PCI总线操作流程:

- 发起者先置REQ #, 当得到仲裁器的许可时( GNT # ),将FRAME #置低电平,并在AD总线上放置Slave地址,同时C/ BE #放置命令信号,说明接下来的传输类型。

- PCI 总线上的所有设备都需对此地址译码,被选中的设备置DEVSEL #以声明自己被选中。然后当IRDY# 与TRDY# 都置低时,传输数据。

- Master在数据传输结束前,将FRAME #置高以标明只剩最后一组数据要传输,并在传完数据后放开IRDY#以释放总线控制权。

PCI EXpress总线

PCI Express是一种完全不同于PCI总线的一种全新总线规范,与PCI总线共享并行架构相比,PCI Express总线是一种点对点串行连接的设备连接方式。点对点意味着每一个PCI E设备都拥有自己独立的数据连接,各个设备之间并发的数据传输互不影响。PCI Express规格从1条通道连接到32条通道连接,有非常强的伸缩性,以满足不同系统设备对数据传输带宽不同的需求。

X1支持双向数据传输,每向数据传输带宽250MB/s; X16即16条点对点数据传输通道连接,X16也支持双向数据传输,每向数据传输带宽高达4GB/s,双向数据传输带宽有8GB/s之多

CPCI总线

为了将PCI总线规范用在工业控制计算机系统上,1995年11月PCI工业计算机制造者联合会(PICMIG)颁布了CompactPCI(以后简称CPCI)规范1.0版。1997年推出了CPCI2.0规范。

CPCI总线规范=PCI总线的电气规范+标准针孔连接器(IEC-1076-4-101)+欧洲卡规范(IEC297/IEEE 1011.1)

I2C

I2C(Inter-Integrated Circuit)总线产生于80年代,最初为音频和视频设备开发。特点是简单有效

- 总线的长度可高达25英尺,并且能够以100Kbps的最大传输速率支持40个组件。

- 支持多主控 (multi master), 其中任何能够进行发送和接收的设备都可以成为主总线。

- 一个主控能够控制信号的传输和时钟频率。

总线的构成及信号类型 :

- I2C总线是由数据线SDA和时钟SCL构成的串行总线

- 在CPU与被控IC之间、IC与IC之间进行双向传送,最高传送速率100kbps。

- 在信息的传输过程中,I2C总线上并接的每一模块电路既是主控器(或被控器),又是发送器(或接收器),这取决于它所要完成的功能。

- CPU发出的控制信号分为地址码和控制量两部分,地址码用来选址。

I2C总线在传送数据过程中共有三种类型信号,它们分别是:开始信号、结束信号和应答信号。

- 开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

- 结束信号:SCL为低电平时,SDA由低电平向高电平跳变,结束传送数据。

- 应答信号:接收数据的IC在接收到8bit数据后,向发送数据的IC发出特定的低电平脉冲,表示已收到数据。

SPI总线

SPI总线接口一般使用4条线:

- 串行时钟线(SCK)

- 主机输入/从机输出数据线MISO

- 主机输出/从机输入数据线MOST

- 低电平有效的从机选择线SS

- 有的SPI接口芯片带有中断信号线INT、或有的SPI接口芯片没有主机输出/从机输入数据线MOSI

存储器

存储器包括主存和外存,大多数嵌入式系统的代码和数据都存储在处理器可以直接访问的存储空间即主存中。

输入输出设备和接口

- 中断控制器、DM、串行和并行接口

- 定时器、计数器、看门狗、RTC、UARTs、PWM

- AD/DA、显示器、键盘